Projects

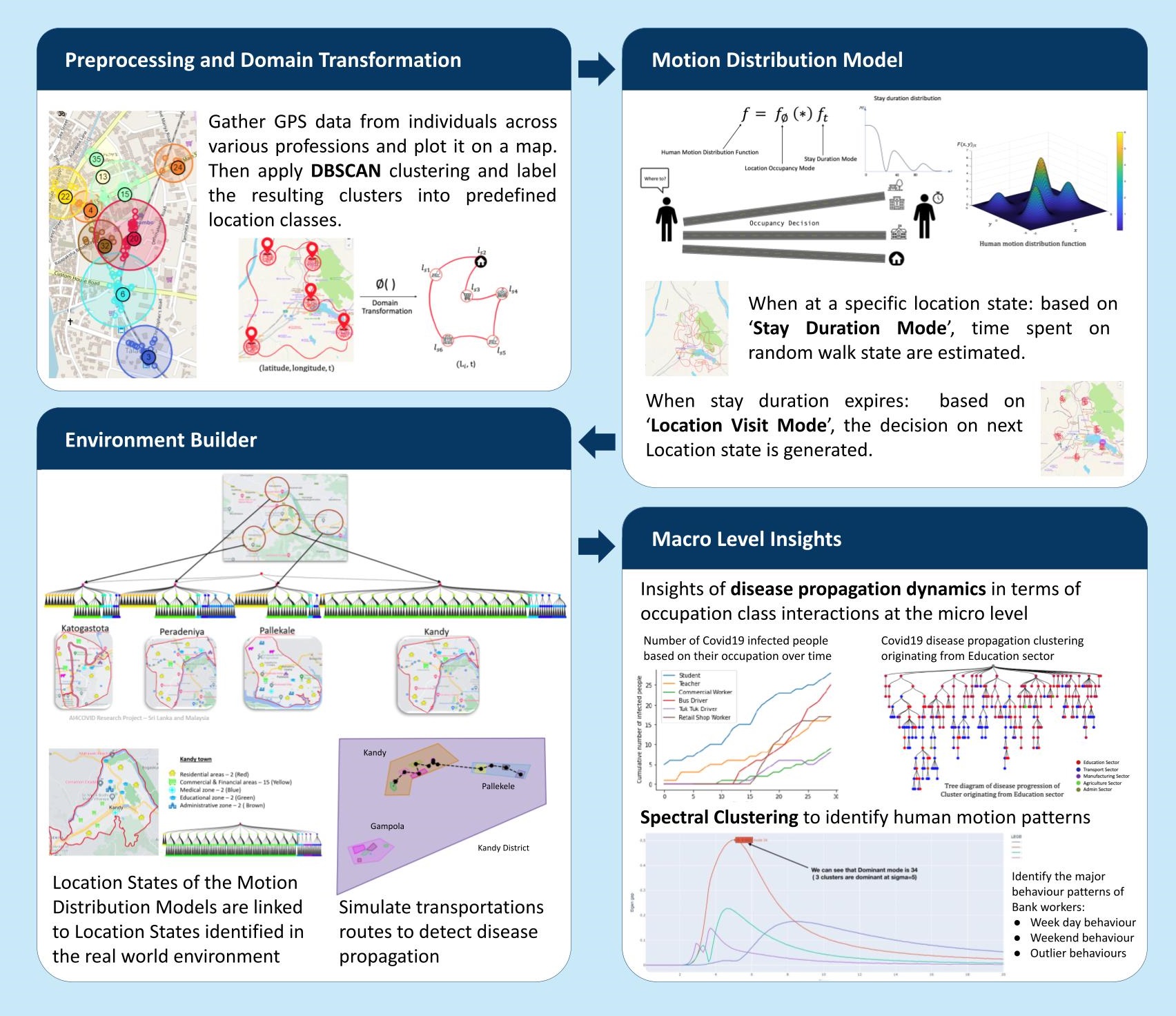

Agent-Based Modelling for Social and Behavioural Dynamics and Impact Assessment (On going)

Group: Sashini Liyanage, G.P. Thennakoon, R. Thiksiga, K.P. Jayasooriya, M. C. L. De Silva, M.M. Viduranga, R. Rodrigo

Modelling human behaviour by utilizing GPS data along with mathematical models and advanced machine learning algorithms within Agent-based Models (ABMs)

- Methods: DBSCAN clustering, spectral clustering, data structure and algorithms, mathematical models

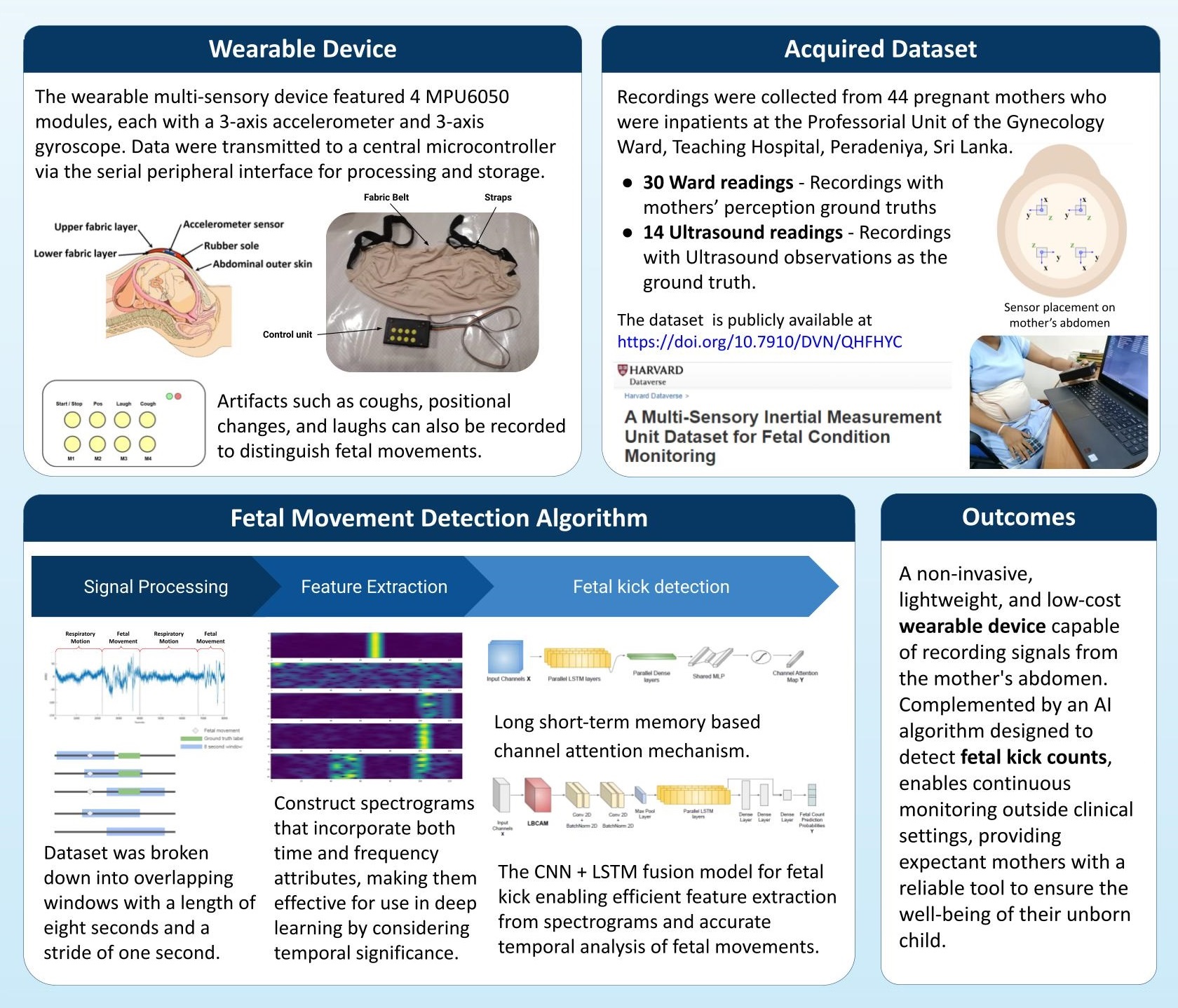

Non-Invasive Accelerometric Based Systems for Fetal Movement Monitoring

Group: Praditha Alwis, Isuru Thilaksiri, Rahal Nanayakkara, Sashini Liyanage

A non-invasive, lightweight, and low-cost wearable device capable of recording signals from the mother's abdomen. Complemented by an AI algorithm designed to detect fetal kick counts, enables continuous monitoring outside clinical settings, providing expectant mothers with a reliable tool to ensure the well-being of their unborn child.

- Methods: Signal filtering, STFT, LSTM, CNN

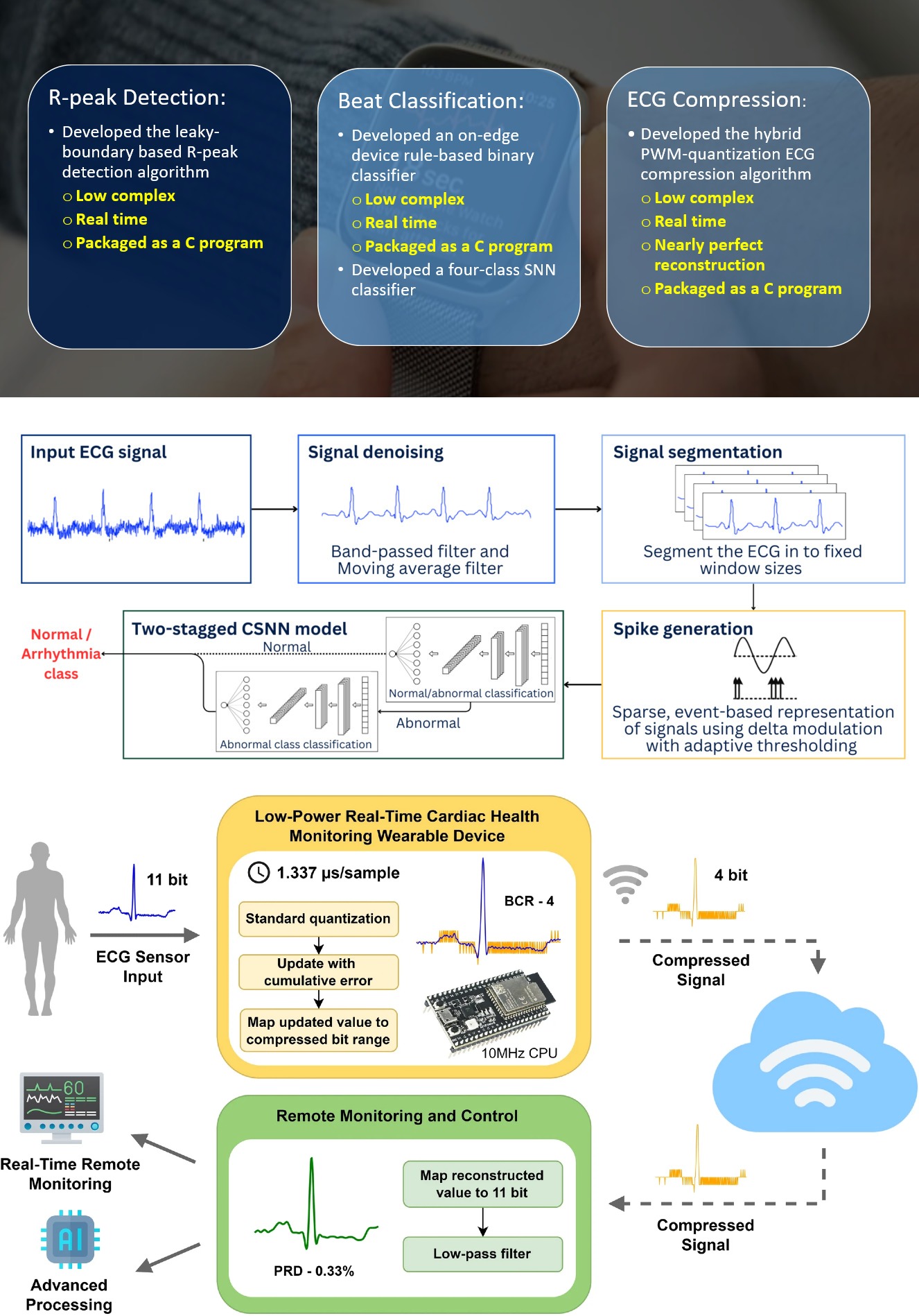

Low-complexity Algorithm for Arrhythmia Detection

Github | Project Page | Nature - Scientific Reports Publication

Group: Sashini Liyanage, Isuri Devindi

A pre-packaged software solution containing a set of low-complexity algorithms for QRS-peak detection and ECG signal compression addressing the null-power consumption environments, along with a Spiking Neural Network implementation to classify ECG beats based on arrhythmia conditions.

- Methods: Signal filtering, Leaky-boundary based QRS-peak detection, Quantization, Spiking Neural Networks

Oral Cancer Prediction System from White Light Images

Poster | Youtube | Dataset | IEEE Access Publication | Elsevier - Oral Oncology Publication

Group: Sashini Liyanage, Achintha Harshamal, Isuri Devindi, Dinura Dissanayake

A web-based tool to reduce the delay in diagnosing high-risk oral cancer patients by incorporating an automated oral cancer prediction model trained on a white light image database derived from the Sri Lankan population.

- Technologies: DenseNet and an XGBoost classifier, React.js, Express.js, flask framework

- Contribution: Development of a web-based annotation tool and Development of the ensemble machine learning model to predict oral cancer using multiple data sources such as images and risk factors.

Reconstructing highly degraded license plates

Group: Sashini Liyanage, Aminda Amarasinghe, Isuri Devindi, N. Varnaraj

A procedure to extract a number plate from an image and reduce several noises due to low resolution, high or low lighting, and motion blur to reconstruct highly degraded images of license plates.

- Technologies: Python, OpenCV, EasyOCR

- Techniques: Morphological transformation, Contouring, Spatial, and Frequency domain filtering

Remote Proctoring Device

Group: Sashini Liyanage, Isuri Devindi, Savindu Wannigama

A single device that integrates the hardware and software components needed to conduct an examination in online mode with no technical interruption.

- Technologies: ReactJS, ElectronJs, Nodejs, MongoDB, Rest API, AWS

- Contribution: Desktop app development, Hardware design

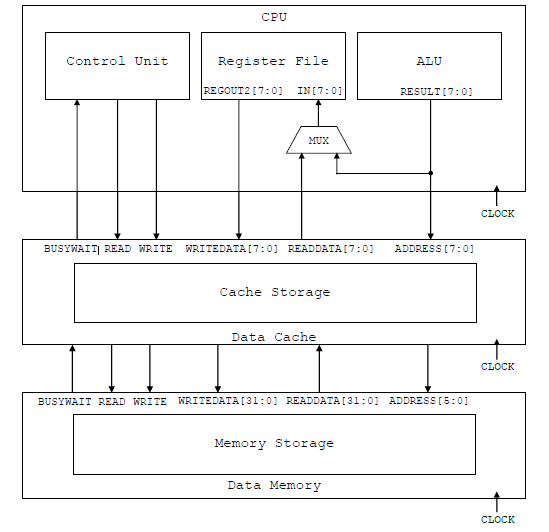

8-bit single cycle processor

Group: Sashini Liyanage, Madhushan Ramalingam

Implement a simple 8-bit single-cycle processor which includes a CPU with a data memory unit and data cache using Verilog HDL

- Technologies: Verilog-HDL

Hobby Projects

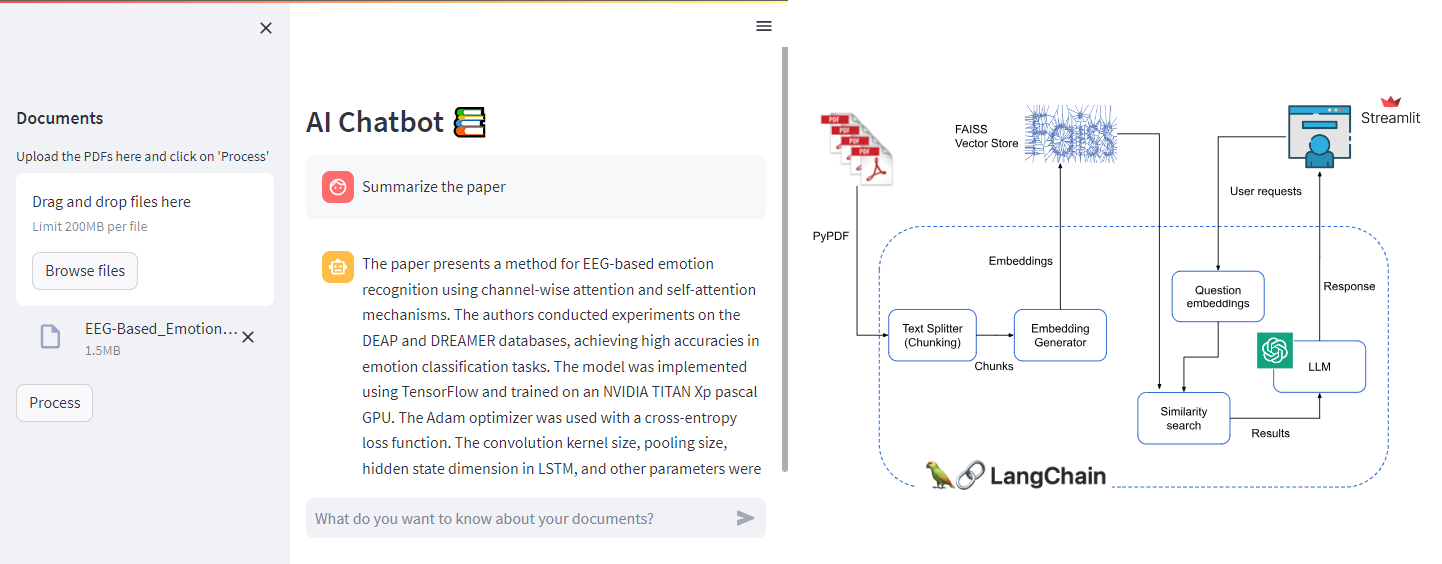

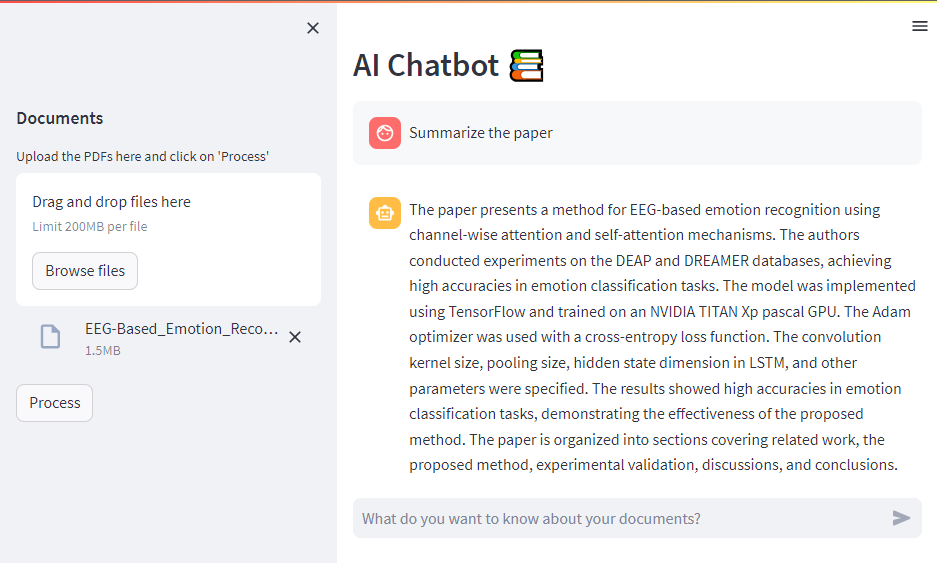

AI Chatbot

Sashini Liyanage

The chatbot is designed as an interactive conversational agent that answers queries and provides information based on the content of uploaded documents.

- Technologies: LangChain, FAISS Vector Store, OpenAI API, Streamlit

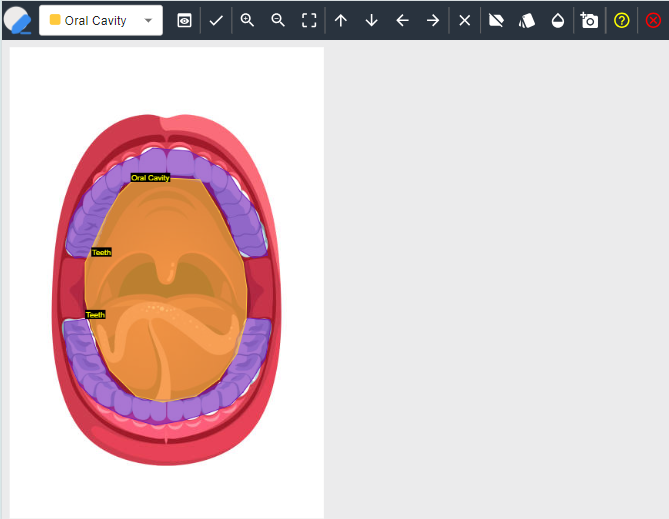

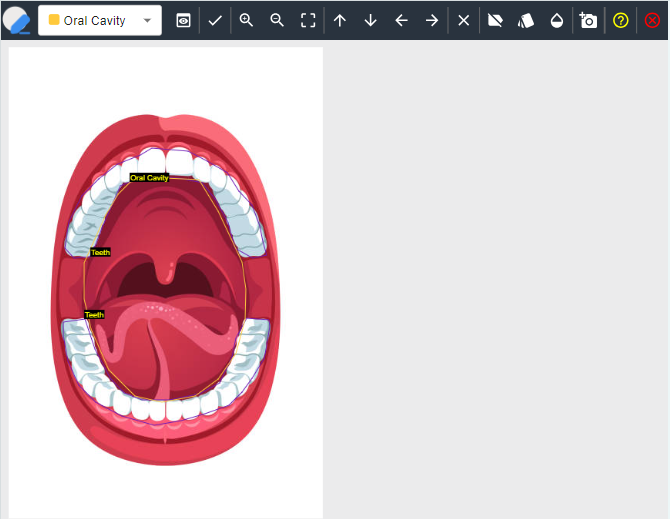

Image Annotator

Sashini Liyanage

The Image Annotator is specifically designed for oral image annotation but can be used for annotating any type of image. Feel free to use it and explore my open-source code for your needs. Annotator © 2023 by Sashini Liyanage is licensed under CC BY 4.0.

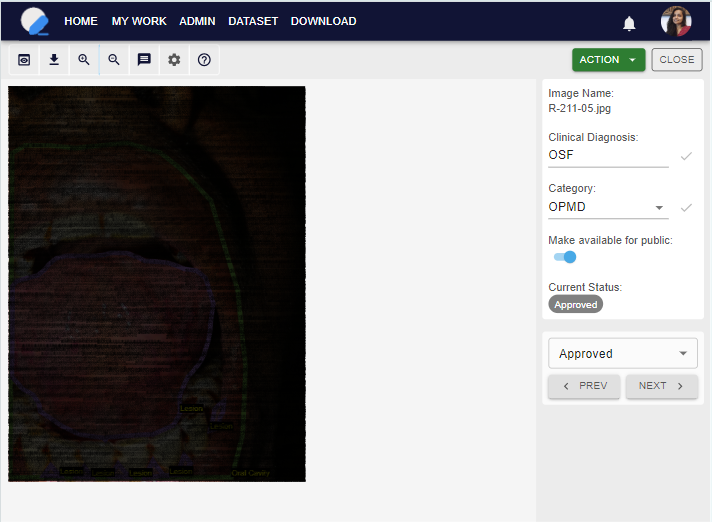

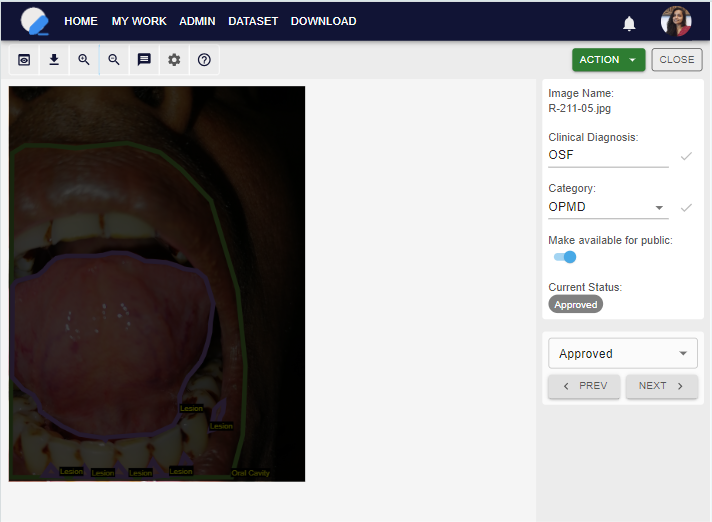

Oral Assessment Screening Iteractive System - Annotator

Sashini Liyanage

Oral Assessment Screening Interactive System (OASIS) is a more sophisticated software solution designed for dental practitioners to collect patients' oral images and annotate them to prepare datasets for machine learning models. It can manage images, share annotated images with reviewers, receive feedback, and track edit history.